#### Implement and Test a Curriculum Around the i281e CPU

sdmay25-31

Ariana Dirksen, Gigi Harrabi, Tessa Morgan, Ethan Uhrich Professor Alexander Stoytchev

# **Team Composition**

- Ethan Uhrich

- Team Lead

- Treasurer

- Computer Engineer

- Ariana Dirksen

- Editor

- Note Taker

- Computer Engineer

- Tessa Morgan

- Task Manager

- Webmaster

- Computer Engineer

- Gigi Harrabi

- Client Interaction Lead

- Outreach Coordinator

- Computer Engineer

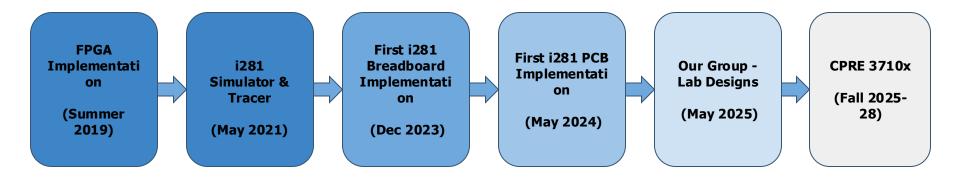

## **Historic Timeline**

### **FPGA Implementation-** Summer 2019

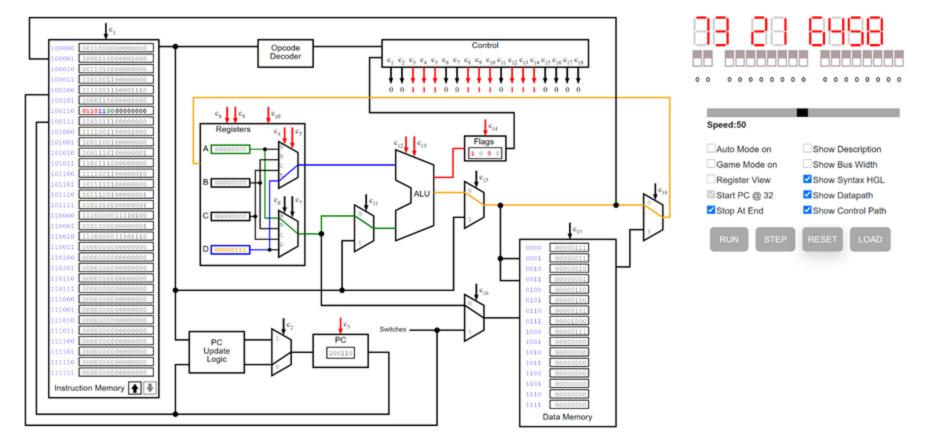

### Simulator - May 2021

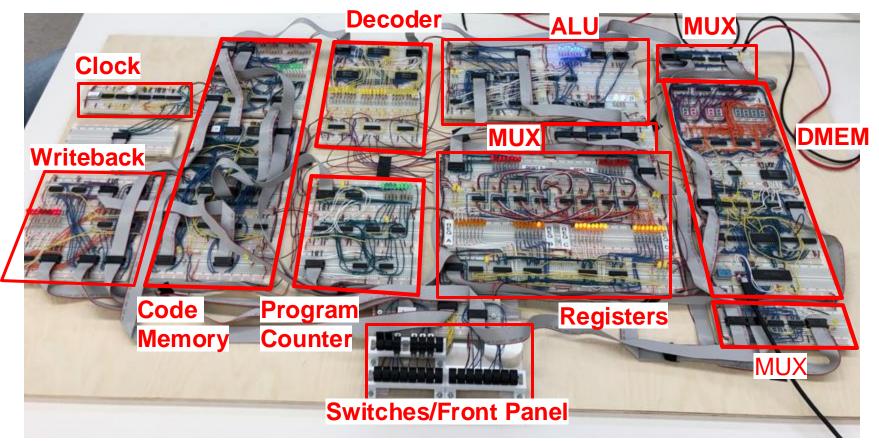

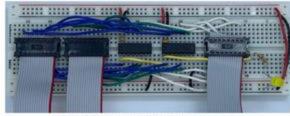

## Breadboard Implementation - Dec 2023 to Feb 2024

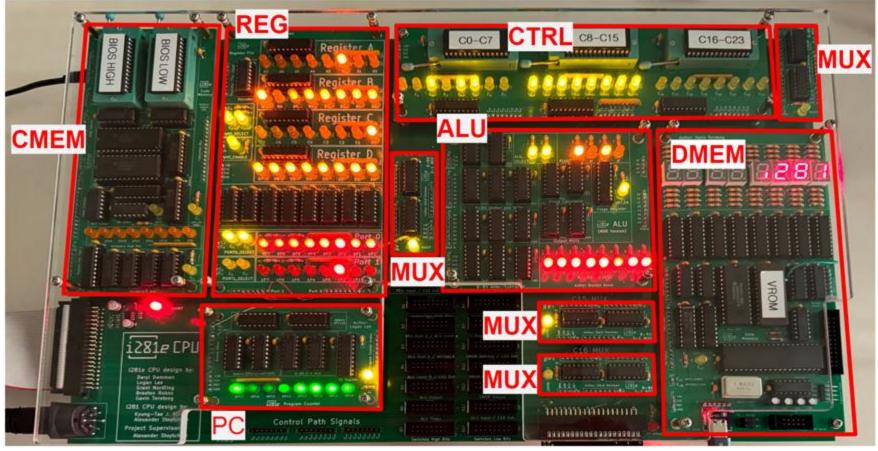

### PCB Implementation - May 2024

### i281e Processor Specifications

- Clock Speed: 1Hz up to 2MHz (up to 2.5MHz overclock)

- Processor fails around 2.75MHz

- Power Requirements: 0.8A @ 5VDC (Input 5-12VDC)

- Fuse for overcurrent protection @ 2A

- Memory: 32 KW (64 KB) of Code RAM, 32 KB of Data RAM

- Also includes 128 words of Code ROM for booting the system

- Compact Flash: extended memory for long-term storage

- Acts as the "hard disk" and stores the OS and File System for DOS/281

## **Existing Resources**

- GitLab

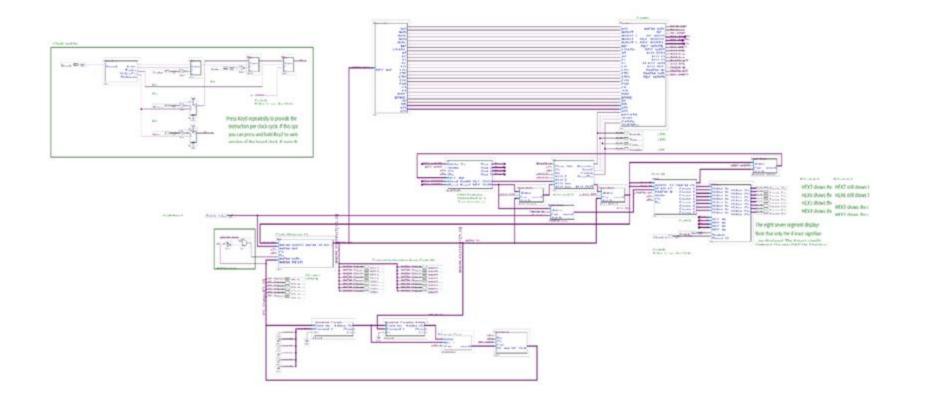

- PCB Schematics

- User Manual

- Electronics and Technology Group (ETG)

- Breadboard Implementation

- Previous Team Websites

- CprE 281 Lectures

- Professor Stoytchev

#### Chapter 4: i281e Programming

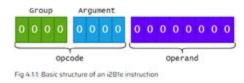

#### 4.1: Structure of an Instruction

Between different instruction set architectures, there is a wide diversity in how machine code instructions are encoded. Different processors employ a wide range of techniques to balance performance, memory consumption, and technical limitations. Some, like the MIPS processor, try to make instruction formats as simple as possible to reduce decoding times. Others, like the xB6 family of processors, include a wide variety of valid instructions to make the most of each execution cycle. A modern x88–54 processor can execute 981 unique instructions, ranging from one to fifteen bytes long.

The i281e does not come close to that in terms of complexity. Each instruction is exactly 16 bits long. It is fetched, executed, and terminated in exactly one clock cycle. Not every instruction ends up using all 16 bits but keeping them at that length helps keep the i281e conceptually simple. An instruction can be breken up into two parts.

- Opcode: The highest 8 bits, which are sent to the control table and is used to generate the control signals for that instruction. This, along with the flag inputs, determines what the processor does during a specific clock cycle. The control table is the only part of the processor to receive the opcode.

- Operand: The lower 8 bits, which are sent to C<sub>17</sub> and C<sub>15</sub> to be used in the data path of the processor. The operand has no influence on what the control signals are during the instruction execution cycle. On the hardware, the value is known as the "immediate Value."

The opcode inself can be broken up further. The top 4 bits of the opcode determine what "group" of instruction executes. Groups are a vague category that tump similar instruction together to ease decoding logic complexity. Some instruction groups contain several similar functions, while most contain only one. The bottom 4 are used as arguments to augment the function of that instruction further.

# **Overview and Requirements**

## **Project Summary**

- Goal: Take these open source hardware and software designs and implement a set of curriculum and outreach activities around them

- Each activity will be tested and documented in detail

- These documents could also be used as educational materials for existing classes or to support future lectures and labs

- A subset of these materials will be used for outreach activities

- Implement another i281e CPU on PCB and document the process

### **Project Summary Cont.**

- Design, create and test at least 10 labs/activities based around the i281e processor completable within a lab period

- To be incorporated into a new class tentatively referred to as:

- CprE 3710x : Microprocessors and Digital Circuits

# **CprE 3710x Timeline by Week**

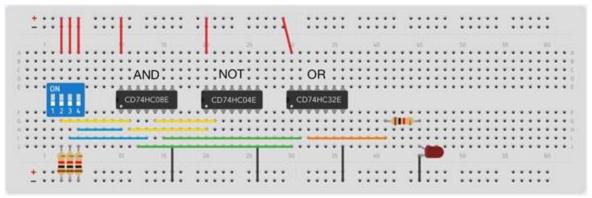

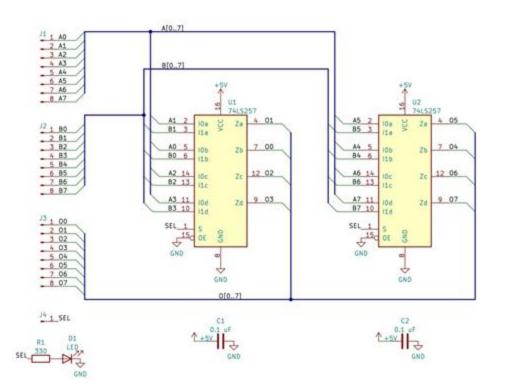

- 1. Intro to Breadboards: 2-to-1 MUX

- 2. Debouncing, LEDs, Resistors

- 3. Standardization and Connectors: Bus MUX

- 4. Introduction to KiCAD

- 5. Mini-Project: MUX in KiCAD and order PCB

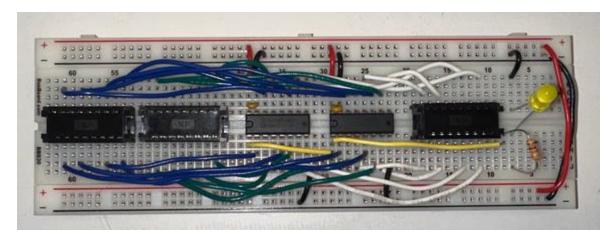

- 6. Program Counter Pt 1: Logic Debugging

- 7. Program Counter Pt 2: Hardware Debugging

- 8. EEPROMs: Program 7-Segment Decoder

- 9. Clock Circuit + Final Project Proposal

- 10. Assembly Level Programming

- 11. Video Game in Assembly

- 12. Peripheral Devices

- 13. Thanksgiving Break

- 14. Final Project Pt 1

- 15. Final Project Pt 2

# **CprE 3710x Timeline by Week**

- 1. Intro to Breadboards: 2-to-1 MUX

- 2. Debouncing, LEDs, Resistors

- 3. Standardization and Connectors: Bus MUX

- 4. Introduction to KiCAD

- 5. Mini-Project: MUX in KiCAD and order PCB

- 6. Program Counter Pt 1: Logic Debugging

- 7. Program Counter Pt 2: Hardware Debugging

- 8. EEPROMs: Program 7-Segment Decoder

- 9. Clock Circuit + Final Project Proposal

- 10. Assembly Level Programming

- 11. Video Game in Assembly

- 12. Peripheral Devices

- 13. Thanksgiving Break

- 14. Final Project Pt 1

- 15. Final Project Pt 2

# Considerations

### Users

### Primary

- Prof. Stoytchev (Client)

- Curriculum

- Past i281 CPU Work

- Undergraduate Students

- Previous knowledge

- Time constraints

- Lab room constraints

### Secondary

- Teaching Assistants

- Outreach Coordinators (WiSE)

- Middle and High School students

## Hardware

Chips:

- Need to be available with plenty of stock for the labs

- Some chips used in i281e processor no longer in production (EEPROM)

- Need to find replacements that are pin compatible to processor

#### Wiring:

- The lab room for the class might not allow for cutting wires

- Wire kits have limited lengths and colors

- Some hardware, like the power supply may short, causing delays in testing

W27C512-45Z-ND Winbond Electronics W27C512-45Z IC EEPROM 512KBIT PARALLEL 28DIP

EEPROM Memory IC 512Kbit Parallel 45 ns 28

W27C512-45Z Models

### Software

### **Ordering Parts**

- Parts for the labs were ordered through ETG

- For microchip specifications, master BOM from i281e group was used for simplicity and compatibility between our modules and the processor

- Used websites like Digikey to find required information for the ETG to get these parts ordered

- Each order took about a week to a week and a half to arrive

# **Progress and Future Plans**

### **Gantt Chart**

| Milestones                              | September | October | November | December | January | February | March | April | May |

|-----------------------------------------|-----------|---------|----------|----------|---------|----------|-------|-------|-----|

| Research i218e processor                |           |         |          |          |         |          |       |       |     |

| Lab 3: Standardization: Bus MUX         |           |         |          |          |         |          |       |       |     |

| Lab 6 & 7: Program Counter              |           |         |          |          |         |          |       |       |     |

| Lab 1: Intro to Breadboards: 2-to-1 MUX |           |         |          |          |         |          |       |       |     |

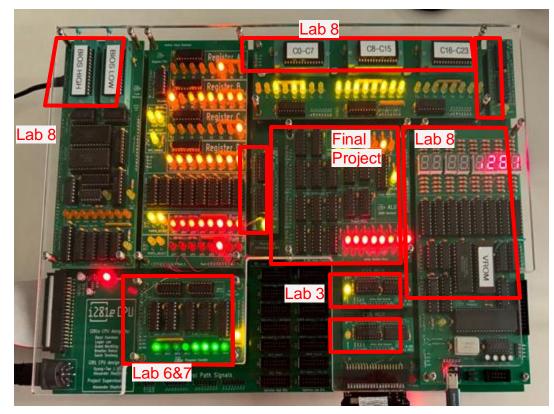

| Lab 8: EEPROMs: 7-Segment Decoder       |           |         |          |          |         |          |       |       |     |

| Lab 2: Debouncing, Specs, Hardware      |           |         |          |          |         |          |       |       |     |

| Lab 4 & 5: KiCAD & Mini-Project         |           |         |          |          |         |          |       |       |     |

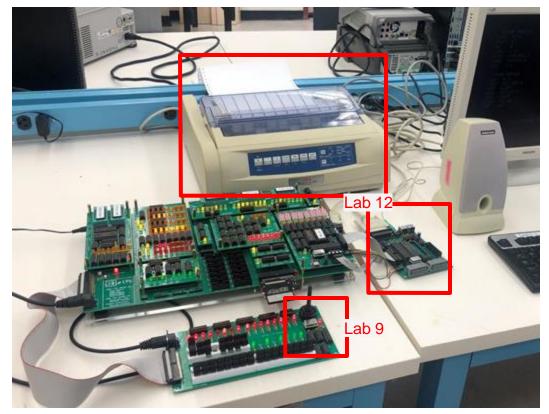

| Lab 9: Clock                            |           |         |          |          |         |          |       |       |     |

| Lab 10: Assembly Programming            |           |         |          |          |         |          |       |       |     |

| Lab 11: Video Game                      |           |         |          |          |         |          |       |       |     |

| Lab 12: Peripherals                     |           |         |          |          |         |          |       |       |     |

| Final Project                           |           |         |          |          |         |          |       |       |     |

| Build i281 CPU (PCB)                    |           |         |          |          |         |          |       |       |     |

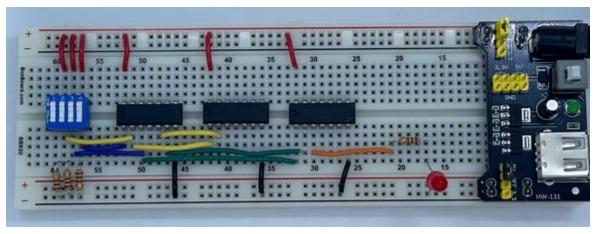

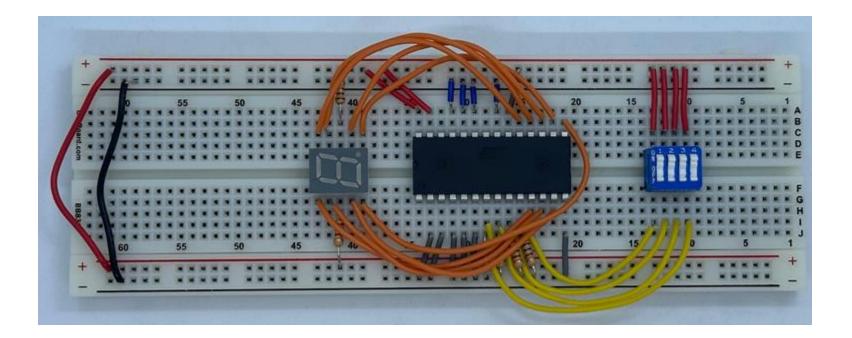

### Lab 1: Bitwise MUX

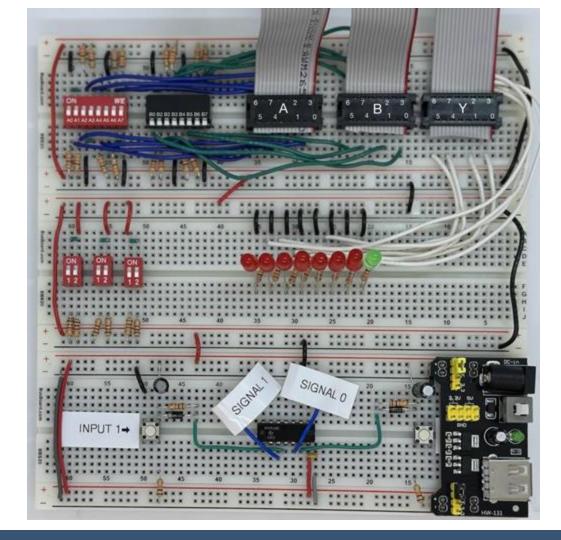

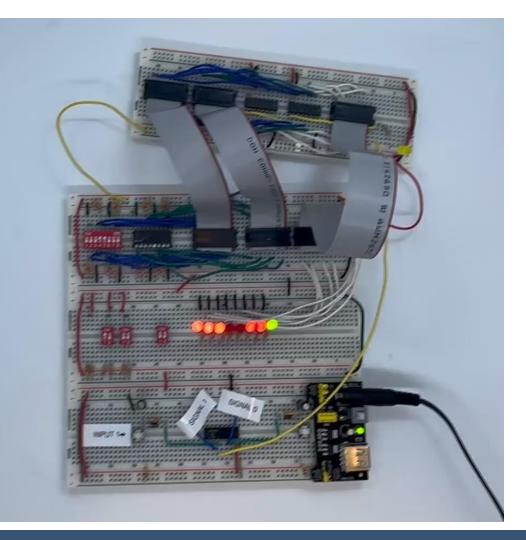

### Lab 1: Demo

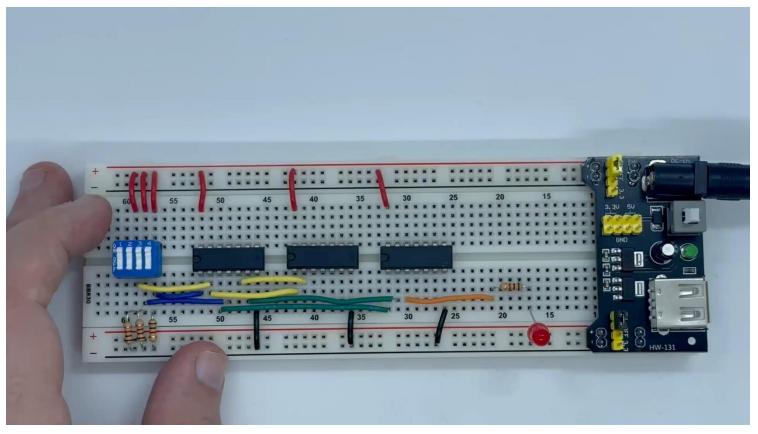

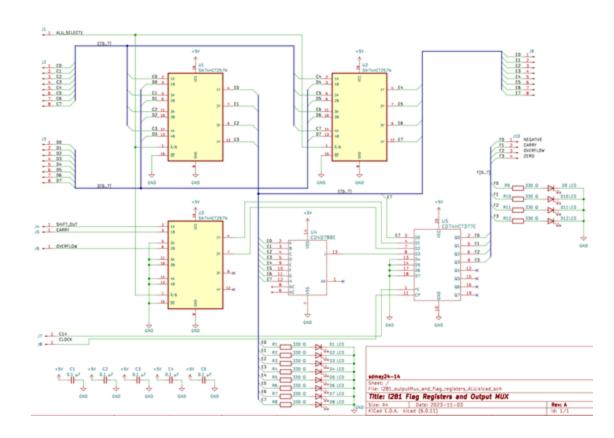

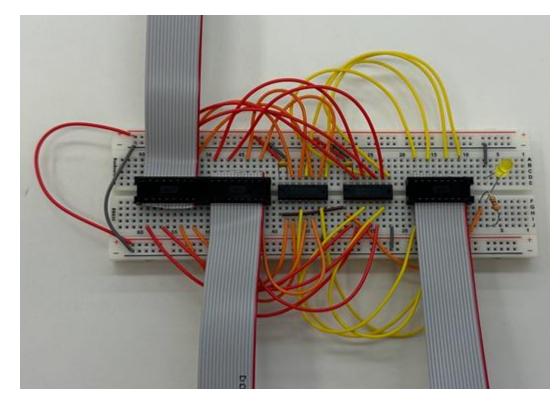

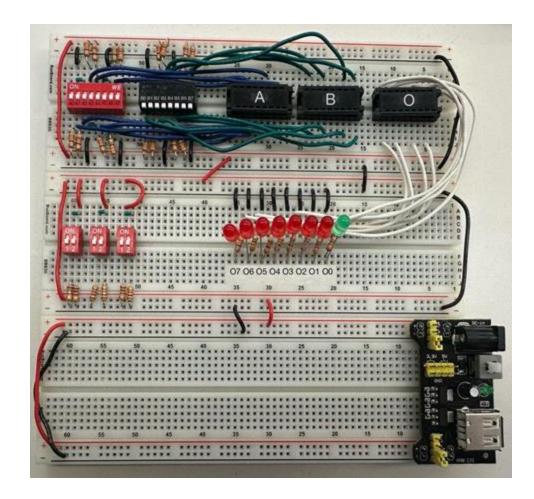

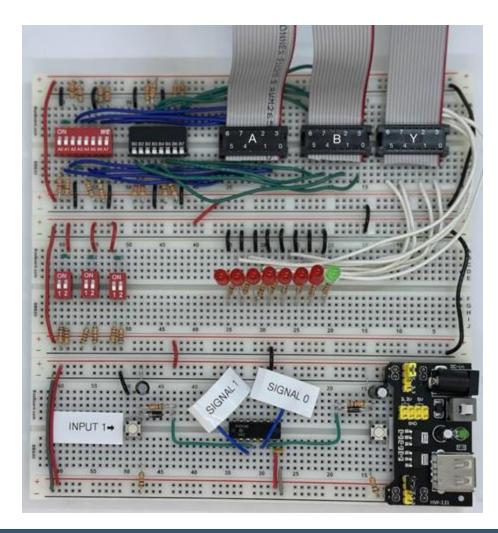

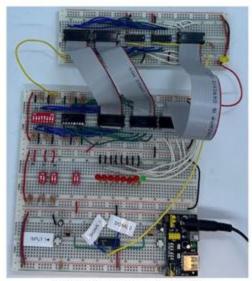

### Lab 3: Bus MUX

### **Tester Circuit**

### Bus MUX Demo

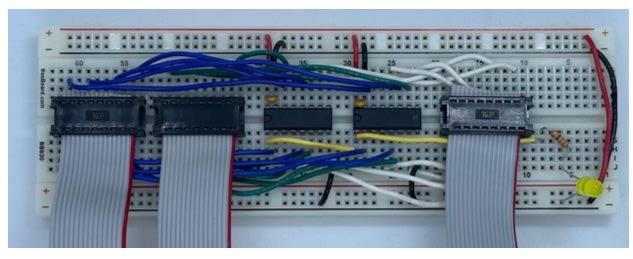

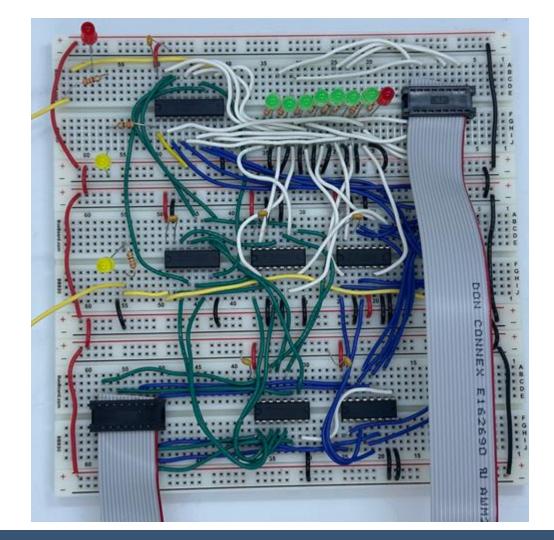

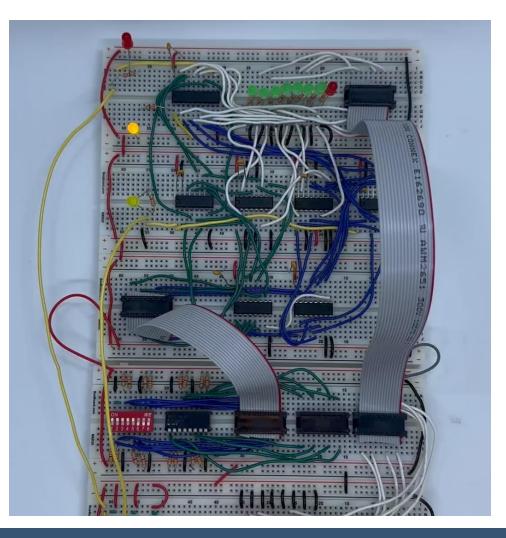

# **Program Counter**

### **Program Counter Demo**

### **7-Segment Decoder with EEPROM**

# **Assembly Level Programming**

- Implement a video game in assembly

- Rock, Paper, Scissors

- Inputs with push buttons

- Score and timing visualized by 7-segment display

- Modify program to be appropriate difficulty

|              | 0x-0                | 0x-1              | 0x-2              | 0x-3              | Øx-4              | ex-s                | 0x-6              | 0x-7              | ex-s              | @x-9              | ex-A                | ex-8              | ex-C              | ex-D              | Øx-E              | Øx-F                |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|-------------------|---------------------|

| 0x0-         | BANK A+*            |                   |                   |                   | BAKK 8+*          |                     |                   |                   | BANK C+*          |                   |                     |                   | BANK D+*          |                   |                   |                     |

| 0x1-         | INPUTC [*]          | INPUTOF<br>[A+*]  | INPUTD [*]        | INPUTOF<br>[A+*]  | CACHE A           | INPUTCP<br>[0+*]    | HRITE<br>[8+*],A  | INPUTOF<br>[8+*]  |                   | INPUTOF<br>[C+*]  | HRITE<br>[C+*],A    | INPUTOF<br>[C+*]  |                   | INPUTCF<br>[D+*]  | WRITE<br>[D+*],A  | INPUTOF<br>[D+*]    |

| ex2-         | NOV A,A<br>NOOP     | HOV A,8           | MOV A,C           | MOV A,D           | NOV B,A           | HOV 8,8<br>NOOP     | MOV B,C           | MOV 8,0           | MOV C,A           | MOV C,8           | MOV C,C<br>NOOP     | MOV C,D           | MOV D,A           | NOV D,8           | MOV D,C           | MOV D,D<br>MOOP     |

| 0x3-         | LOADI A,*           |                   |                   |                   | LONDE 8,*         |                     |                   |                   | LOADI C,*         |                   |                     |                   | LOADI D,*         |                   |                   |                     |

| <b>e</b> x4- | ADD A,A<br>SHEFTL A | ADD A.8           | ADD A,C           | ADD A,D           | ADD 8,A           | ADD 8,8<br>SHIFTL 8 | ADD 8,C           | ADD 8,0           | ADD C,A           | ADD C,8           | ADD C,C<br>SHEFTL C | ADD C,D           | ADD D,A           | ADD 0,8           | ADD D,C           | ADD D,D<br>SHIFTL D |

| exs-         | ADDI A,*            |                   |                   |                   | ADDI 8,*          |                     |                   |                   | ADDI C,*          |                   |                     |                   | ADDE D,*          |                   |                   |                     |

| @x6-         | SUB A,A             | SUB A,8           | SUB A,C           | SUB A,D           | 508 B,A           | sue e,e             | sue e,c           | SUB 8,0           | SUB C,A           | sue c,e           | sue c,c             | SUB C,D           | SUB D,A           | SUB 0,8           | SUB D,C           | SUB D,D             |

| 8x7-         | SUBI A,*            |                   |                   |                   | SUBI 8,*          |                     |                   |                   | SUBI C,*          |                   |                     |                   | SUBI D,*          |                   |                   |                     |

| ex8-         | LOAD A,[*]          |                   |                   |                   | LOAD 8,[*]        |                     |                   |                   | LOAD C,[*]        |                   |                     |                   | LOAD D,[*]        |                   |                   |                     |

| 8x9-         | LOADF A, [A+*]      | LOADF A, [8+*]    | LOADF A,<br>[C+*] | LOADF A, [D+*]    | LOAD# B,<br>[A+*] | LOADF 8,<br>[8+*]   | LOADF B,<br>[C+*] | LOAD# 8,<br>[0+*] | LOAD# C,<br>[A+*] | LOAD# C,<br>[8+*] | LOADF C,<br>[C+*]   | LOAD# C,<br>[0+*] | LOAD# D,<br>[A+*] | LOAD# D,<br>[8+*] | LOAD# D,<br>[C+*] | LOAD# D,<br>[D+*]   |

| exA-         | STORE<br>[*],A      |                   |                   |                   | STORE<br>[*],8    |                     |                   |                   | STORE<br>[*],C    |                   |                     |                   | STORE<br>[*],D    |                   |                   |                     |

| 0×8-         | STOREF<br>[A+*],A   | STOREF<br>[8+*],A | STOREF<br>[C+*],A | STOREF<br>[0+*],A | STOREF<br>[A+*],8 | STOREF<br>[8+*],8   | STOREF<br>[C+*],8 | STOREF<br>[D+*],8 | STOREF<br>[A+*],C | STOREF<br>[8+*],C | STOREF<br>[C+*],C   | STOREF<br>[D+*],C | STOREF<br>[A+*],D | STOREF<br>[8+*],D | STOREF<br>[C+*],D | STOREF<br>[D+*],D   |

| exc-         | MORI A,*            | SHEFTR A          |                   |                   | MORI B,*          | SHEFTR B            |                   |                   | NORI C,*          | SHEFTR C          |                     |                   | NORI D,*          | SHIFTR D          |                   |                     |

| exp-         | CHP A,A             | CHP A,8           | CHP A,C           | CHP A,D           | OP 8,A            | CIP 8,8             | 09 8,C            | CHP 8,0           | 09 C,A            | CHP C,8           | 09 c,c              | CHP C,D           | CIP 0,A           | 09 0,8            | CHP 0,C           | CHP 0,0             |

| ext-         | NOR A,A             | NOR A,8           | NOR A,C           | NOR A,D           | NOR B,A           | NOR 8,8             | NOR B,C           | NOR 8,0           | NOR C,A           | NOR C,8           | NOR C,C             | NOR C,D           | NOR D,A           | NOR D,8           | NOR D,C           | MOR D,D             |

| exF-         | BRC *               | BRNC *            | 880 *             | BRND *            | BRN *             | BRNN *<br>BRP *     | BRZ *<br>BRE *    | BRNZ *<br>BRNE *  | 88A *             |                   | 886 *               | BRGE -            | BRL *             | BRLE *            | JUMPR C+*         | 389.1               |

# **Final Project**

- Write a Device Driver

- Implement a Register File

- Implement the ALU w/ modifications

- Design a peripheral device

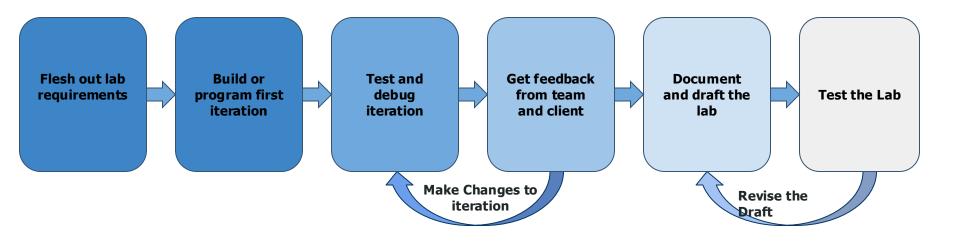

# **Design Iterations**

# Flesh Out Lab Requirements

- What do we want to accomplish with this lab?

- Teach students how to implement a hardware Bus

- Familiarize students with CPU component

- What do the students need to learn?

- What is a Bus?

- What is Standardization?

- How can we accomplish this?

- Have the students make a component they've already learned about, but as a Bus

# **Build Our First Iteration**

- Using wires with predetermined length we implemented the logic

- Based our design off of the 2-to-1

8-bit Bus Multiplexers from the i281 breadboard implementation

# **Test and Debug Circuit**

- Needed to test the circuit to verify that the circuit works as expected

- Created a testing circuit

# **Test and Debug Circuit**

• Through testing our tester circuit we found that the tester needed debouncing added to account for implementations that use clocks

# **Get Feedback from Team and Client**

Used Cut Wires to Standardize Colors:

- Input A as blue

- Input B as green

- Output as white

- Select as yellow

- Power as red

- Ground as black

# **Document and Draft the Lab**

- Documented circuit design and began creating instructions

- Added relevant background information and pre-lab

- Finalize testing procedure

- Get feedback from client

- Repeat

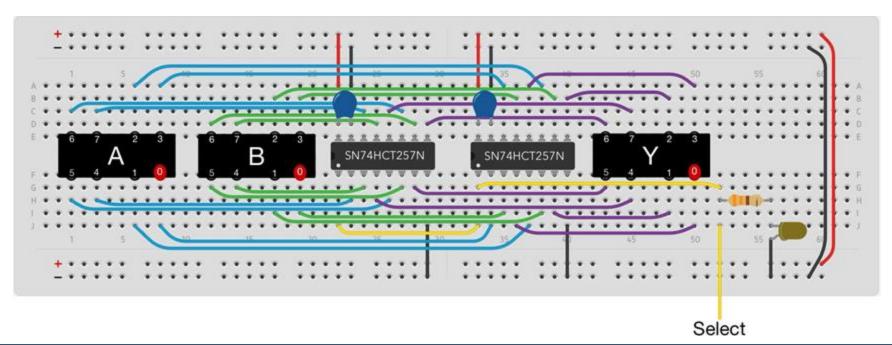

Lab 3 Mux lab, intro to buses, standardization and connectors

#### 1.0 Objectives

In this lab we will be recreating the two to one 8-bit bus multiplexer from the i281e processor using physical hardware. This lab covers the concepts of hardware buses, hardware circuit standardization and connection.

#### 2.0 Background

#### 2.1 Buses

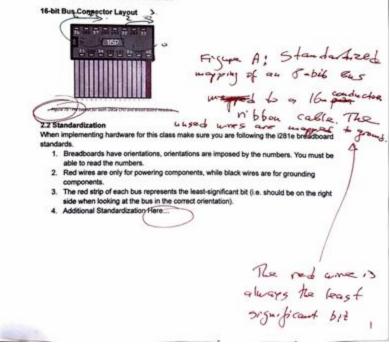

In hardware buses are represented as 16-bit connectors. The connector's we use within this lab are laid out according to the image below. Please note that the red line on the wire should always be placed to indicate the lowest bit.

# Test the Lab

- Have some volunteers follow along the lab

- See how long it takes them

- Get feedback

#### Prelab

1. What is the operating voltage for the SN74HCT257N Pin?

#### CprE 3710x Lab 3 Electrical and Computer Engineering Iowa State University

### Bus Multiplexer and Intro to Standardization and Connectors

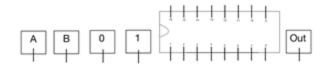

On the diagram below, connect inputs A and B to any MUX on the SN74HCT257N chip. Connect the output of the MUX to the box labeled "Out" and use the '0' or '1' to select A as the output.

#### Lab

4.1 Verify that you placed your chips, connectors, power and ground wires correctly. Show your progress on the breadboard implementation to the TA before you proceed.

TA Initials: \_\_\_\_\_

4.3 Verify that you connected the inputs to the SN74HCT257N(MUX) chips correctly. Show your progress on the breadboard implementation to the TA before you proceed.

TA Initials:

4.5 Verify that you connected the outputs from the SN74HCT257N(MUX) chips to the output connector correctly. Also, verify that you connected the select wire to the SN74HCT257N(MUX) chips and the LED. Make sure that the cathode of the LED is connected to ground. Show your completed breadboard implementation to the TA before you proceed.

TA Initials: \_\_\_\_\_

CprE 3710x Lab 3

Electrical and Computer Engineering Iowa State University

# Bus Multiplexer and Intro to Standardization and Connectors

#### 1.0 Objectives

In this lab, you will recreate the two-to-one 8-bit bus multiplexer from the i281e processor on a breadboard. This lab also covers the concepts of hardware buses, hardware circuit standardization, and connectors.

#### 2.0 Parts List

| Quantity | Items                                                                          |                  |

|----------|--------------------------------------------------------------------------------|------------------|

| 1        | White 830-point Breadboard                                                     |                  |

| Set of   | Breadboard Wire Spools                                                         | Pre Cut Wire Kit |

| 1        | Wire Cutters Electronic Grade                                                  | 7                |

| 1        | Wire Strippers Electronic Grade                                                |                  |

| 2        | Quad 2-1 MUX (SN74HCT257N) Chips                                               |                  |

| 2        | 0.1 uF Ceramic Capacitor                                                       |                  |

| 1        | 5mm Yellow LED                                                                 |                  |

| 1        | 330 Ω THT Resistor                                                             |                  |

| 3        | Connectors, 16 position ribbon cable, DIP header connector IDC through<br>hole |                  |

| 3        | Connectors, 16 position rectangular receptacle connector IDC                   |                  |

| 3        | 8 to 12 inches Ribbon Cable                                                    |                  |

#### CprE 3710x Lab 3 Electrical and Computer Engineering Kowa State University

### Bus Multiplexer and Intro to Standardization and Connectors

#### 3.0 Background

#### 3.1 8-bit Buses

Figure 3 shows an 8-bit bus implemented with a 16-conductor ribbon cable. Because we have twice as many wires than we need half of which are not used. Figure 1 shows the mapping of the wires to the 16-position connector. The unused wires are labeled with G. Figure 2 shows the pins of the connector designed to plug into the breadboard. Please note that the red wire indicates the least significant bit.

Figure 1: Standardized mapping of an 8-bit bus to a 16 conductor ribbon cable.

Figure 2: Side view of the connector pins.

Figure 3: An 8-bit bus with connectors on both sides.

#### CprE 3710x Lab 3 Electrical and Computer Engineering Iowa State University

### Bus Multiplexer and Intro to Standardization and Connectors

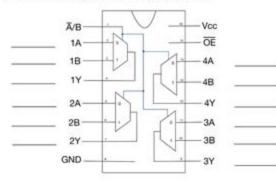

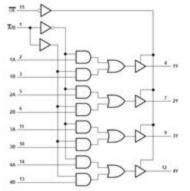

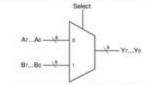

To implement the 8-bit 2-to-1 bus multiplexer, you will use two SN74HCT257N chips. As shown in Figure 4 each of them contains four 2-to-1 multiplexers that share the same select line. To complete the entire circuit, we need to combine two of the chips and a select line to choose between the two input buses  $A = (A_0 \dots A_0)$  and  $B = (B_1 \dots B_0)$ .

The output bus is called Y = (Y7 ... Yo).

Please refer to the datasheet for additional information about the SN74HCT257N chip.

Figure 6: Pin layout for the Quad 2-to-1 MUX Chip (SN74HCT257N).

#### 3.2 Standardization

When implementing circuits for this class, ensure you follow the following breadboard standards:

- Each Breadboard has an orientation imposed by the numbers. You must be able to read the numbers. (i.e., they are not upside down).

- 2. Red wires are only for powering components, while black wires are for grounding.

- The red wire on each ribbon cable represents the least significant bit (i.e., it should be on the right side when looking at the ribbon cable in the correct orientation).

- 4. When visualizing a 8-bit binary number with LEDs, the least significant bit should always be on the right side when you look at the breadboard from the correct orientation.

#### CprE 3710x Lab 3 Electrical and Computer Engineering

Bus Multiplexer and Intro to Standardization and Connectors

#### 3.3 Implementation

A 8-bit 2-to-1 bus MUX is typically drawn as shown in Figure 3. This expands into Figure 4 to show the individual 2-to-1 multiplexers, which have the same select input.

Figure 4: Graphical symbol for a 2-to-1 bus MUX (8-bits wide).

#### CprE 3710x Lab 3 Electrical and Computer Engineering Iowa State University

## Bus Multiplexer and Intro to Standardization and Connectors

#### 4.0 Activity

Please complete the pre-lab before starting with the lab. Specifically, you need to understand which pins go where and the orientation of the chips.

#### 4.1 Place the Bus Connectors and the Chips

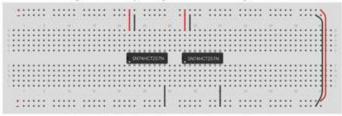

- Place the chips as shown in Figure 6.

- Connect them to power (pin 16) and ground (pin 8).

- Connect OE (pin 15) to ground.

- Place the three bus connectors as shown in Figure 7.

#### Before continuing to the next step, have your circuit checked by a TA.

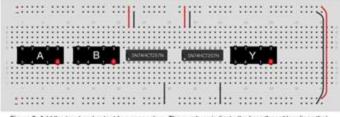

Figure 7: Place the chips and connect them to power and ground. Also connect their output enable pin to ground (pin 15,  $\overline{OE} = 0$ ).

Figure 8: Add the input and output bus connectors. The numbers indicate the breadboard locations that correspond to the data lines.

#### CprE 3710x Lab 3 Electrical and Computer Engineering Iowe State University

### Bus Multiplexer and Intro to Standardization and Connectors

#### 4.4 Connect the Output pins

Start by connecting the four most significant bits (left chip) to the output:

- Top: Connect pins 9 and 12 on the chip to bits Y6 and Y7, respectively.

- Bottom: Connect pins 4 and 7 on the chip to bits Y4 and Y5, respectively.

Next, connect the least significant bits (right chip) to the output

- Top: Connect pins 9 and 12 on the chip to bits Y2 and Y3, respectively.

- Bottom: Connect pins 4 and 7 on the chip to bits Y0 and Y1, respectively.

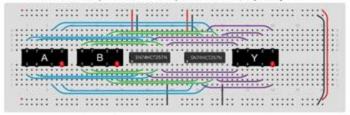

Figure 11: Connect the wires to the output bus (purple wires).

#### 4.5 Finish the Circuit

- Place an LED on the right side of the circuit and ground it.

- Connect the anode of the LED to a 330 Ω resistor. This pin should also be connected to the select input, which may be grounded for now but will connect to the test circuit later.

- Connect the other side of the resistor to both chips at pin 1 (yellow wires in Figure 11).

- Place two 0.1 µF capacitors connecting pins 15 and 16 of each chip.

CprE 3710x Lab 3 Decrical and Computer Engineering

### Bus Multiplexer and Intro to Standardization and Connectors

#### 4.6 Make Three Ribbon Cables with Connectors

- Next, line up the ribbon with the connector so each connector pin is in contact with one bit of the ribbon.

- Once the ribbon is in place, firmly press down with a flat object until it clicks into place.

#### 4.7 Connect the Ribbon Cables to the MUX

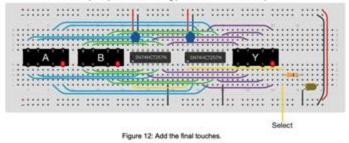

- Figure 14 shows the completed circuit. At this point it uses 3 connectors as placeholders. They are not connected to anything at this point.

- Start with the breadboard upright (the numbers are readable facing you) and replace the connectors with a connector that already has a ribbon cable attached to it. The ribbon should go out the bottom of the breadboard with the red wire on the right side.

- Repeat these steps with the other two ribbons and connectors on your MUX.

Figure 14: The finished bus MUX with place-holder connectors.

Figure 15: The finished bus MUX with ribbon cables attached.

#### CprE 3710x Lab 3 Dectrical and Computer Engineering towa State University

### Bus Multiplexer and Intro to Standardization and Connectors

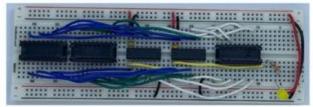

#### 5.1 Connect the Ribbon Cables to the Tester Circuit

- Place your Bus MUX circuit above the tester circuit. Input A is the leftmost connector on the MUX and tester.

- Repeat this for bus B and the output bus Y.

- Next, connect the select line. To do this, use the select line that was grounded in step 4.5 to a switch on the tester circuit.

Figure 16: Bus MUX circuit connected to tester circuit.

# Conclusion

- 10+ lab activities for a new CprE 3710x class

- Have two labs finalized and progress on three others

- Our labs consist of a mix of digital logic and hardware

- There is a timeline worked out for finishing all the labs

- Also plan to build another PCB implementation